LCIS Valence

Laboratoire de Conception et d'Intégration des Systèmes

Laboratoire de Recherche de Valence

+60 chercheurs de l’Université Grenoble Alpes et de Grenoble INP-UGA

Nos actualités

Jeudi 14 mars après midi, un groupe de 15 lycéens de 2nde option SL (Sciences et Laboratoire) du Lycée Triboulet de Romans-sur-Isère, accompagnés par 2 enseignant(e)s de Physique-Chimie, sont venus...

Bienvenue à Meng Yang, le nouveau doctorant de l'équipe ORSYS depuis le 1er novembre 2023. Il est encadré par Nicolas Barbot. Son bureau est au bâtiment AB, 2e étage, A222.

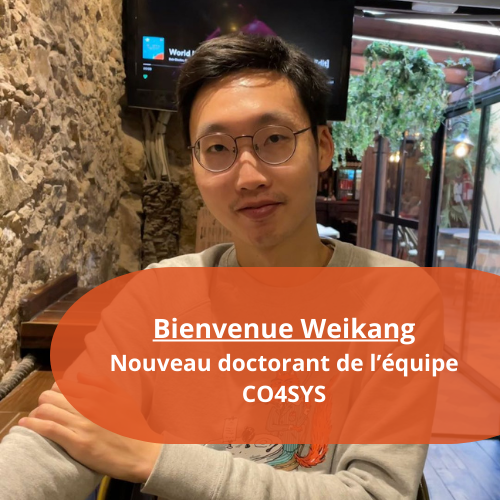

Bienvenue à Weikang Zeng, le nouveau doctorant de l'équipe Co4Sys depuis le 23 octobre 2023. Il est encadré par Michel Occello, François Suro et Clément Raievsky. Son bureau est au...

Duc Tri VO, a second year PhD candidate at LCIS, has obtained the Best Student Paper Award at the 20th International Conference on Informatics in Control, Automation and Robotics (ICINCO)...

Ihab Alshaer s’est vu remettre le Best Paper Award lors de la 22ème Conférence CARDIS (Smart Card Research and Advanced Application Conference)

Lors de la 21eme édition ``IEEE European Control Conference’’ qui s'est tenue à Bucarest (12-16 juin 2023) avec plus de 450 participants du monde entier, diverses activités scientifiques ont été...

Nos évènements

Le laboratoire en quelques mots

Le LCIS est un laboratoire de recherche public, équipe d’accueil de l’Université Grenoble Alpes associée à Grenoble-INP sur le campus UGA Valence.

Le LCIS rassemble plus de 60 chercheurs en informatique, électronique et automatique autour des systèmes embarqués et communicants.

Les thématiques abordées concernent la sûreté et la sécurité des systèmes embarqués et distribués, la modélisation, l’analyse et la supervision des systèmes complexes ouverts et les systèmes radiofréquences sans fil communicants.

Le laboratoire travaille sur des domaines d’application variés : internet des objets, systèmes cyber-physiques, environnements connectés naturels ou artificiels, RFID, etc.

Le LCIS est soutenu et financé par la région Auvergne-Rhône-Alpes

UN LABORATOIRE A LA NOTORIÉTÉ INTERNATIONALE

Les travaux du LCIS sur les systèmes embarqués et communicants sont régulièrement présentés dans les plus grandes conférences scientifiques internationales. Ces travaux concernent la spécification, la modélisation, la conception, la communication, la sûreté, la sécurité et le diagnostique de ces systèmes.

- Une équipe internationale – Nos chercheurs et doctorants viennent du monde entier

- Des offres de thèses – De nombreux étudiants préparent leur thèse dans notre laboratoire

- Une équipe pluridisciplinaire – 26 enseignants-chercheurs issus de Grenoble INP- Esisar et de l’IUT de Valence , de 20 à 30 doctorants, des post-doctorants et des collaborateurs de recherche.

Nos équipes de recherche

ORSYS

Systèmes RF sans fil communicants

Les travaux de recherche développés au sein de l’équipe ORSYS s’articulent autour de l’utilisation des technologies et signaux radiofréquences (RF), sans fil/ (Wireless), pour la communication, le traitement des signaux et la mesure.

ORSYS s’intéresse tout particulièrement aux systèmes passifs de transmission d’information basés sur les principes de rétro-modulation et rétrodiffusion des ondes électromagnétiques. Parmi les systèmes étudiés citons les systèmes sans fil/sans contact (Wireless) telles que les technologies RFID et l’Ultra Large Bande (UWB).

CO4SYS

Coordination, Coopération, Contrôle des systèmes complexes

L’équipe CO4SYS travaille sur la modélisation, la commande et la supervision des systèmes complexes artificiels.

L’équipe s’intéresse aux systèmes multi-agents physiquement distribués dans lesquels cohabitent des agents aux capacités réactives et cognitives, devant trouver des compromis entre des objectifs locaux et globaux potentiellement incompatibles, raisonnant avec des connaissances partielles du système global et devant assurer un routage dynamique et non sûr de la communication. Ce paradigme permet l’intégration d’approches complémentaires provenant de l’intelligence artificielle collective et de la théorie du contrôle.

CTSYS

Sûreté et Sécurité des systèmes embarqués et distribués

Le groupe CTSYS est constitué de chercheurs de différentes disciplines (électronique, informatique, télécom) qui étudient les différents éléments des systèmes embarqués : du matériel à l’application. Une attention particulière est portée à l’interaction entre le matériel et le logiciel.

Les principaux domaines applicatifs des recherche du groupe sont : l’internet des objets (dont les systèmes RFID), les réseaux de capteurs, les environnements Smart-* (-Home, -Building, -Car, etc.), l’industrie des transports…

LES EQUIPES ET RECHERCHES

Découvrir

EVENEMENTS ET ANIMATIONS

Découvrir

LES ACTUALITES

Découvrir

Nos partenaires et collaborations

Ils ont travaillé avec le laboratoire et ont profité du savoir et de l’expertise de nos équipes de recherches.

Collaborez avec plus de 60 chercheurs au LCIS

Entreprise, futur doctorant ou chercheur, contactez-nous pour plus d’information